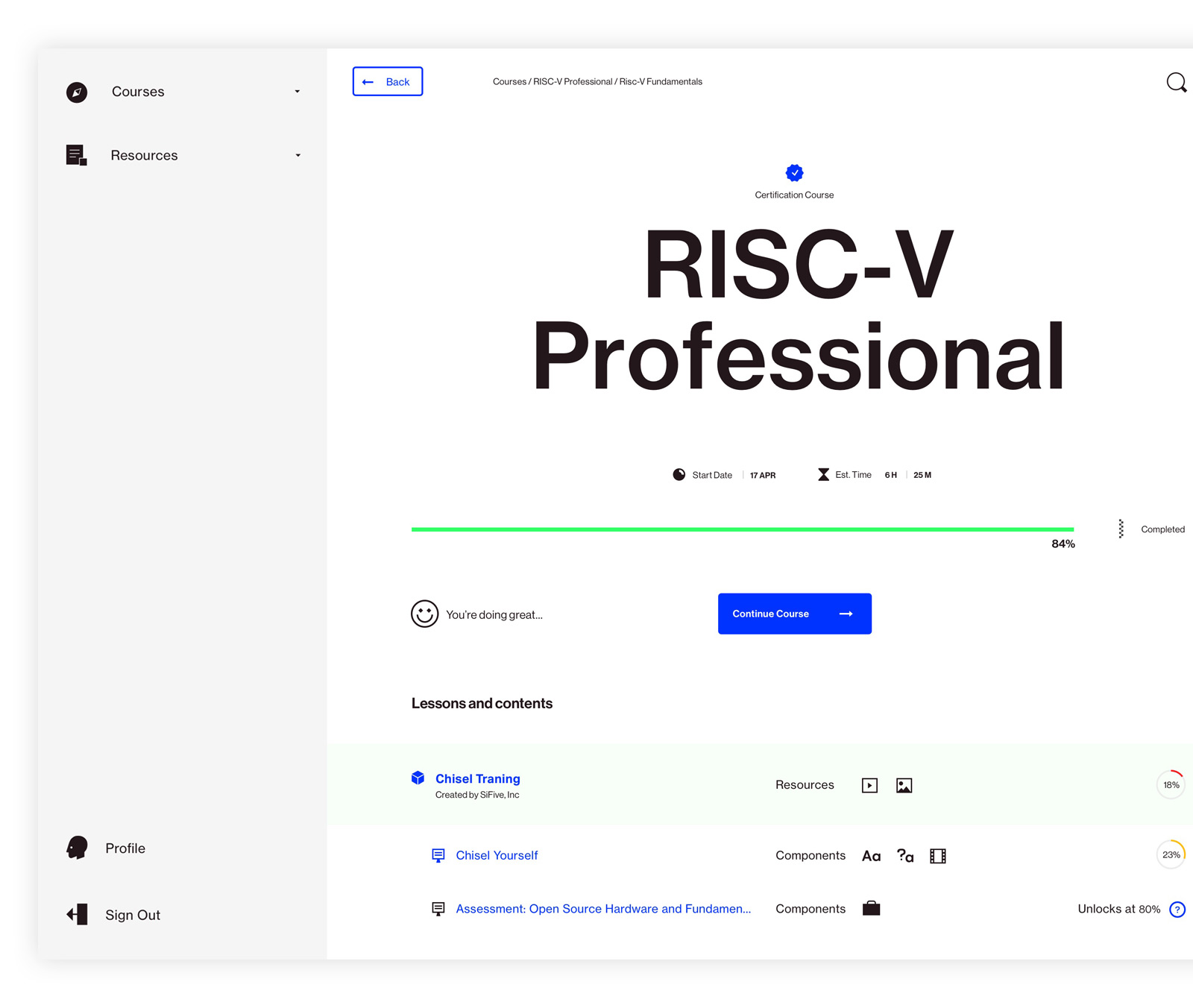

The SiFive RISC-V course is based on world-leading content taught at UC Berkeley, where the open-source RISC-V ISA was first designed in 2010, and where our co-founder Krste Asanović teaches as a Professor in the Computer Science Division of the EECS Department.

Krste Asanovic

Co-Founder & Chief Architect

In addition to his role at SiFive, Krste is a Professor in the EECS Department at the University of California, Berkeley, where he leads the RISC‑V ISA project and serves as the Co-Director for the ADEPT Lab, and is Chairman of the RISC‑V Foundation.

Krste received his PhD in Computer Science from UC Berkeley.

Andrew Waterman

Co-Founder & Chief Engineer, SiFive

Andrew received his PhD in Computer Science from UC Berkeley, where, weary of the vagaries of existing instruction set architectures, he co-designed the RISC‑V ISA and the first RISC‑V microprocessors with Yunsup Lee. Andrew is one of the main contributors to the open-source RISC‑V based Rocket chip generator and the Chisel project.

Yunsup Lee

Co-Founder & CTO, SiFive

Yunsup received his PhD in Computer Science from UC Berkeley, where he co-designed the RISC‑V ISA and the first RISC-V microprocessors with Andrew Waterman, and led the development of the Hwacha decoupled vector-fetch extension.

Invite your students & assign content to your class

Create your own content from scratch or by re-using platform content

Learners can follow courses & submit assessments